# High-Speed Board Designs

June 1996, ver. 1

Application Note 75

#### Introduction

To create a successful high-speed printed circuit board (PCB), you must integrate the device(s), PCB(s), and other elements into a coherent design. Most Altera devices have user-controllable slew rates, some of which can be as high as 1 to 3 ns. This would contribute to noise generation, signal reflection, cross-talk, and ground bounce. Therefore, your design must:

- Filter and evenly distribute power to all devices to reduce noise

- Terminate signal and transmission lines to diminish signal reflection

- Minimize cross-talk between parallel traces

- Reduce the effects of ground bounce

# Power Filtering & Distribution

You can dramatically reduce system noise by providing clean, evenly distributed power supply as close as possible to  $V_{CC}$  to all boards and devices.

#### **Filtering Noise**

To diminish the low-frequency (< 1 kHz) noise caused by the power supply, you must filter the noise on the power lines at the point where the power connects to the PCB, and where it connects to each device. Altera recommends placing a 100- $\mu$ F electrolytic capacitor immediately adjacent to the location where the power supply lines enter the PCB. If you use a voltage regulator, place the capacitor immediately after the final stage that provides the  $V_{CC}$  signal to the device(s). Capacitors not only filter low-frequency noise from the power supply, but also supply extra current when many outputs switch simultaneously in a circuit.

The components on the PCB add high-frequency noise to the power plane. To filter high-frequency noise at the device, Altera recommends placing 0.02- $\mu F$  and 0.2- $\mu F$  decoupling capacitors as close as possible to each  $V_{CC}$  and GND pair.

See the *Operating Requirements for Altera Devices Data Sheet* in this data book for more information on bypass capacitors.

**Altera Corporation**

A-AN-075-01

**368 7703000 25372**

445

#### **Distributing Power**

Power distribution also has an impact on system noise. Power can be distributed throughout the PCB with either a power bus network or power planes.

A power bus network consists of two or more wide, metal traces that carry the  $V_{CC}$  and GND to the devices. Usually used on two-layer PCBs, power buses provide an inexpensive method of supplying power. The trace widths, which should be as wide as possible, are limited by the density of the PCB. Power buses have significant DC resistance; the last component on the bus may receive  $V_{CC}$  power that is degraded by as much as 0.5 V. Consequently, Altera recommends using power buses only for applications that do not require an equal distribution of  $V_{CC}$ .

As an alternative, Altera recommends using power planes to distribute power. Power planes are used on multi-layer PCBs and consist of two or more metal layers that carry  $V_{CC}$  and GND to the devices. Because the power plane covers the full area of the PCB, its DC resistance is very low. The power plane maintains  $V_{CC}$  and distributes it equally to all devices, while also providing near-infinite current-sink capability, noise protection, and shielding for the logic signals on the PCB.

## Signal & Transmission Line Termination

Having established the PCB power network, you must consider the layout of the devices and traces. Fast edge rates contribute to noise, cross-talk, and ground bounce to varying degrees, depending on the PCB construction material.

Each PCB substrate has a different relative dielectric constant ( $E_r$ ) that measures the effect of an insulator on the capacitance of a conductor pair compared to the capacitance of the conductor pair in a vacuum. The type of substrate used determines the length at which the signal traces must be handled as transmission lines. Table 1 lists  $E_r$  values for various dielectric materials.

446

**Altera Corporation**

**■** 0595372 0005098 2T4 **■**

| Table 1. Relative Dielectric Constants |                |

|----------------------------------------|----------------|

| Material                               | E <sub>r</sub> |

| Air                                    | 1.0            |

| PTFE/glass                             | 2.2            |

| Rogers RO 2800                         | 2.9            |

| CE/goreply                             | 3.0            |

| BT/goreply                             | 3.3            |

| CE/glass                               | 3.7            |

| Silicon dioxide                        | 3.9            |

| BT/glass                               | 4.0            |

| Polymide/glass                         | 4.1            |

| FR-4/glass                             | 4.1            |

| Glass cloth                            | 6.0            |

| Alumina                                | 9.0            |

The following equation shows how the relative dielectric constant ( $E_r$ ) of the material determines the velocity ( $V_P$ ) at which signals may flow. The constant (C) equals  $3\times 10^8$  m/s or 30 cm/ns:

$$V_P = \frac{C}{\sqrt{E_r}}$$

The signal trace must be treated as a transmission line when the two-way propagation delay (PD) of the line exceeds the signal edge rate  $(t_R)$ . The propagation delay for MAX 9000, MAX 7000, FLASHlogic, MAX 5000, and Classic devices is the input-to-output delay  $(t_{PD})$ . The propagation delay for FLEX 10K and FLEX 8000 devices is either the transfer rate from I/O pin to I/O pin via row, logic element (LE), and column or the transfer rate from I/O pin to I/O pin via row, LE, and row. See the following equation:

$$t_R < 2 \times PD$$

An Altera device's signal edge rate at the rising edge is a function of the capacitance that is driven by the device. You can estimate this signal edge rate if you know the device's capacitive load. Altera device family data sheets include output drive characteristics graphs that show the voltage/current relationship of the output drives. You can derive an equation for signal edge rate at the rising edge as a function of capacitance using these output drive characteristics graphs. Figure 1 shows the output drive characteristics for the MAX 7000 device family.

**Altera Corporation**

447

**■** 0595372 0005099 130 **■**

Figure 1. Output Drive Characteristics of MAX 7000 Devices

The relationship between high-level output current ( $I_{OH}$ ) and output voltage ( $V_O$ ) is roughly linear until the voltage approaches 4 V. The equation for the linear approximation is as follows:

$$I_{OH} = 0.15 - \frac{0.15}{3.8} \times V_{O} = 0.15 - 0.0395 \times V_{O}$$

Solving the charging capacitor equation for time (t) yields the following equations:

$$\frac{\partial \mathbf{V}}{\partial t} = \frac{\mathbf{I}_{\mathrm{OH}}}{C} \qquad \qquad \partial t = \frac{C}{\mathbf{I}_{\mathrm{OH}}} (\partial \mathbf{V})$$

Substituting the equation above for I<sub>OH</sub> yields the following equation:

$$\partial t = \frac{C}{0.15 - 0.0395 V} (\partial V)$$

Integrating and solving the integral from 0 V to 2.4 V yields the following signal edge rate  $(t_R)$  equation for the rising edge:

$$\mathbf{t_{R}} = C \frac{-1}{0.0395} \times \ln(0.15 - 0.0395 \text{ V}) \Big|_{0}^{2.4} = 25.3 \times C$$

You can choose different bounds for the integral if you need to drive a device with an input high voltage ( $V_{IH}$ ) greater than 2.4 V. For instance, if your Altera device is driving a CMOS input,  $V_{IH}$  will increase to 3.84 V, so you can integrate from 0 V to 3.84 V instead of from 0 V to 2.4 V.

448

**Altera Corporation**

**■** 0595372 0005100 782 **■**

To calculate output delay time, you must first determine the rise time of the specified load. At the 35-pF load, the rise time is as follows:

$$\mathbf{t_R} = (25.3)(35 \times 10^{-12}) \sec = 0.9 \text{ ns}$$

The propagation delay (PD) is the length ( $\it{l}$ ) of the line divided by the velocity ( $\it{V}_{\it{P}}$ ):

$$PD = \frac{l}{V_P}$$

By solving for length (*l*) using the equation below, you can calculate the length at which the line must be treated as a transmission line:

$$l > \frac{\mathbf{t_R} \times \mathbf{k}}{2\sqrt{E_r}}$$

As shown in Table 1 on page 447, a PCB with glass cloth substrate has an  $\rm E_r$  of 6. Table 2 lists the maximum line lengths for FLEX 10K, FLEX 8000, MAX 9000, MAX 7000, and MAX 5000 devices using a glass cloth substrate under a 35-pF load.

| Device Family | t <sub>R</sub> (ns) | <i>l</i> (cm) | l (inches) |

|---------------|---------------------|---------------|------------|

| FLEX 10K      | 1.02                | 6.25          | 2.46       |

| FLEX 8000     | 1.1                 | 6.73          | 2.65       |

| MAX 9000      | 0.88                | 5.42          | 2.14       |

| MAX 7000      | 0.9                 | 5.51          | 2.17       |

| MAX 5000      | 2.7                 | 16.52         | 6.50       |

Mismatched impedances cause signals to reflect back and forth, and up and down the line, which in turn causes ringing at the load. To eliminate reflections, the impedance of the source  $(Z_S)$  must equal the impedance of the trace  $(Z_0)$  and the load  $(Z_L)$ .

The load impedance is typically much higher than the line impedance, which is higher than the source impedance. On an unmatched transmission line, a signal reflects 100% at the load and approximately 80% at the source, bouncing back and forth until it dies out. To reduce signal reflection, you can match the impedance either at the load  $(Z_{\rm L})$  or at the source  $(Z_{\rm S})$  to the line impedance  $(Z_{\rm Q})$ . You can match the impedance by adding an impedance in parallel with the load to reduce its input impedance.

**Altera Corporation**

449

**II** 0595372 0005101 619 **I**

### Termination Schemes

Parallel termination diminishes the first reflection by matching the load impedance to the line impedance. The following are four parallel termination circuits. Altera recommends using either the Thevenin or resistor and capacitor (series-RC) scheme. For the matching to be effective, you must terminate each load, because any impedance mismatch will result in a signal reflection.

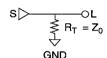

#### **Simple Parallel Termination**

In a simple parallel termination scheme, the terminating resistor  $(R_T)$  is equal to the line impedance. The placement of the termination resistor must be as close to the load as possible to be efficient. The current loading of this termination is highest at a high-output state. You can estimate the current load  $(I_L)$  with the following equation:

$$I_{L} = I_{OH} \times \frac{R_{DS}}{R_{TOTAL}}$$

$R_{DS}$  is the pull-up resistance from the  $I_{OH}$  curve (refer to Figure 1 on page 448) of the output drive characteristic.  $R_{TOTAL}$  is the sum of  $R_{DS}$  and  $R_{T}.$  For example, the current load for a 50- $\Omega$  parallel termination on a MAX 7000 device at 2.4 V is as follows:

$$I_L = 45 \text{ mA} \times \frac{25\Omega}{75\Omega} = 15 \text{ mA}$$

The current load cannot exceed the maximum DC limit per output pin. In this case, the 15-mA current load is less than the maximum DC limit of 25 mA per output pin for MAX 7000 devices.

#### **Thevenin Parallel Termination**

$S > R_1$   $R_1 \parallel R_2 = Z_0$

An alternative parallel termination scheme uses a Thevenin voltage divider. The terminating resistor is split between  $R_1$  and  $R_2$ , which equal the line impedance when combined. Although this scheme reduces the current draw from the source device, it adds current drawn from the power supply because the resistors are tied between  $V_{CC}$  and GND.

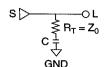

#### **Active Parallel Termination**

In an active parallel termination scheme, the terminating resistor ( $R_T = Z_0$ ) is tied to a bias voltage ( $V_{BLAS}$ ). The bias voltage is selected so that the output drivers are capable of drawing current from the high- and low-level signals. However, this scheme requires a separate voltage source that can sink and retain currents to match the output transfer rates.

450

Altera Corporation

**=** 0595372 0005102 555 |

#### **Series-RC Parallel Termination**

In a parallel termination scheme, a resistor and capacitor (series-RC) network is used as the terminating impedance. The terminating resistor ( $R_T$ ) is equal to  $Z_0$ ; the capacitor must be greater than 100 pF. The capacitor blocks low-frequency signals while passing high-frequency signals. Therefore, the DC loading effect of  $R_T$  does not impact the driver.

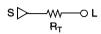

#### **Series Termination**

A series termination scheme matches the impedance at the signal source instead of matching the impedance at each load. Because the output impedance of Altera devices is low, you must add a series impedance to match the signal source to the line impedance.

On an unmatched line, the source eventually reduces the reflections; adding the series termination helps attenuate secondary reflections. The source impedance varies from  $10\,\Omega$  to  $25\,\Omega$ , and the line impedance varies depending on the distribution of the load. Therefore, you cannot choose a single resistor value that applies to all conditions. Altera recommends using a  $33\text{-}\Omega$  series resistor to cover most impedances. This method requires only a single component at the source rather than multiple components at each load, but delays the signal path as it increases the RC time constant.

#### Cross-Talk

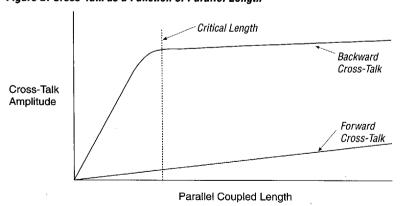

Cross-talk is the unwanted coupling of signals between parallel traces. Two types of cross-talk exist: forward (capacitive) and backward (inductive). Figure 2 illustrates the effect of each type of cross-talk as a function of the parallel length.

Figure 2. Cross-Talk as a Function of Parallel Length

Altera Corporation

451

**3** 0595372 0005103 491

Backward cross-talk, which has a more dramatic effect than forward cross-talk, occurs when the magnetic field from one trace induces a signal in a neighboring trace. In logic systems, the current flow through a trace is significant when the signals are switching or non-static. The magnetic fields created by switching currents induce the coupling transients.

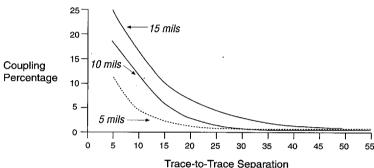

You can dramatically reduce cross-talk by limiting the trace distance to 10 mils above the GND plane. Figure 3 shows the effect of trace height on trace-to-trace coupling.

Figure 3. Effect of Trace Height on Trace-to-Trace Coupling

#### **Ground Bounce**

As digital devices become faster, their output switching times decrease. Faster switching times cause higher transient currents in outputs as they discharge load capacitances. These higher currents, which are generated when multiple outputs of a device switch simultaneously from a logic high to a logic low, can cause a board-level phenomenon known as ground bounce.

Many factors contribute to ground bounce. Therefore, no standard test method allows you to predict its magnitude for all possible PCB environments. You can only test the device under a given set of conditions to determine the relative contributions of each condition and of the device itself. Load capacitance, socket inductance, and the number of switching outputs are the predominant factors that influence the magnitude of ground bounce in programmable logic devices.

452

**Altera Corporation**

**■** 0595372 0005104 328 **■**

#### **Design Recommendations**

Altera recommends that you take the following steps to reduce ground bounce:

- Turn on the Slow Slew Rate logic option for FLEX 10K, FLEX 8000, MAX 9000, MAX 7000E, and MAX 7000S designs.

- Limit load capacitance by buffering loads with an external device such as the 74244 IC bus driver or by reducing the number of devices that drive the bus.

- Eliminate sockets whenever possible.

- Reduce the number of outputs that can switch simultaneously and/or distribute them evenly throughout the device.

- Move switching outputs close to a package GND pin.

- Eliminate pull-up resistors, or use pull-down resistors.

- Use multi-layer PCBs that provide separate V<sub>CC</sub> and GND planes.

- **■** Add  $10-\Omega$  to  $30-\Omega$  resistors in series to each of the switching outputs to limit the current flow into each of the outputs.

Go to "Slow Slew Rate" using **Search for Help on** (Help menu) in MAX+PLUS II for more information about this logic option.

These design recommendations, many of which are described in detail later in this application note, should help you create effective high-speed logic designs that operate over a wide range of PCB conditions.

#### **Analyzing Ground Bounce**

Figure 4 shows a simple model for analyzing ground bounce. The external components driven by the device appear to that device as capacitive loads (C1 to Cn). These capacitive loads store a charge that is determined by the following equation:

charge (Q) = [voltage (V)  $\times$  capacitance (C)]

Thus, the charge increases as the voltage and/or load capacitance increases.

**Altera Corporation**

453

**=** 0595372 0005105 264 |

Figure 4. Ground Bounce Model

The environment and ground path of a device have intrinsic inductances (shown in Figure 4 as L1, L2, and L3). L1 is the inductance of the bond wire from the device's die to its package pin, and of the pin itself. L2 is the inductance of the connection mechanism between the device's ground pin and the PCB. This inductance is greatest when the device is connected to the PCB through a socket. L3 is the inductance of the PCB trace between the device and the PCB location where the power supply's reference ground is connected.

Ground bounce occurs when multiple outputs switch from high to low. The transition causes the charge stored in the load capacitances to flow into the device. The sudden rush of current  $(\partial i/\partial t)$  exits the device through the inductances (L) to board ground, generating a voltage (V) determined by the equation  $V = L \times (\partial i/\partial t)$ . This voltage difference between board ground and device ground causes the relative ground level for low or quiet outputs to temporarily rise or bounce. Although the rush of current is brief, the magnitude of the bounce can be large enough to trigger other devices on the PCB.

In synchronous designs, ground bounce is less often a problem because synchronous outputs have enough time to settle before the next clock edge. Also, synchronous circuits are not as likely to be falsely triggered by a voltage spike on a quiet output.

Ground bounce is affected differently by capacitive loading on the switching outputs and quiet outputs.

454

**Altera Corporation**

#### **Switching Outputs**

When the capacitive loading on the switching outputs increases, the amount of charge available for instantaneous switching increases, which in turn increases the magnitude of ground bounce. Depending on the device, ground bounce increases with capacitive loading until the loading is approximately 100 pF per device output. At this point, the device output buffers reach their maximum current-carrying capacity and inductive factors become dominant.

One method of reducing the capacitive load, and consequently ground bounce, is to connect the device's switching outputs to a bus driver integrated circuit (IC). The outputs of the bus driver IC drive the heavy capacitive loads, reducing the loading on the device, thus minimizing ground bounce for the device's quiet outputs.

Some bus applications use pull-up resistors to create a default high value for the bus. These resistors cause the load capacitances to charge up to the maximum voltage. Consequently, the driving device produces a higher level of ground bounce. Therefore, you should eliminate pull-up resistors in applications in which ground bounce is a concern, or design a bus logic that uses pull-down resistors instead.

The number of switching outputs also affects ground bounce. As the number of switching outputs increases, the total charge stored also increases. The total charge is equal to the sum of the stored charges for each switching output. Therefore, the amount of current that must sink to ground increases as the number of switching outputs increases. Ground bounce can increase by as much as 40 mV to 50 mV for each additional output that is switching.

To counteract these effects, Altera devices provide multiple VCC and GND pin pairs. You can reduce ground bounce by moving switching outputs close to a package GND pin, and by distributing simultaneously switching outputs throughout the device.

Many Altera devices have slew rate options for the output drivers. Turning on the Slow Slew Rate option for all or most of the drivers slows down the drivers, decreasing  $\partial i/\partial t$  and reducing ground bounce.

To further reduce ground bounce, limit the number of outputs that can switch simultaneously in your design. For functions such as counters, you can use Gray coding as an alternative to standard sequential binary coding, since only one bit switches at a time.

Altera Corporation

455

**=** 0595372 0005107 037 **=**

In extreme cases, adding resistors (10  $\Omega$  to 30  $\Omega$  is usually adequate) in series to each of the switching outputs in a high-speed logic device can limit the current flow into each of the outputs, and thus reduce ground bounce to an acceptable level.

#### **Quiet Outputs**

An increase in capacitive loading on quiet outputs acts as a low-pass filter and tends to dampen ground bounce. Capacitive loading on a quiet output can reduce ground bounce by as much as 200 to 300 mV. However, an increase in capacitive loading on a quiet output can increase the noise seen on other quiet outputs.

#### **Minimizing Lead Inductance**

Socket usage and PCB trace length are two elements of L2, the inductance of the connection mechanism between the device's ground pin and the PCB shown in Figure 4 on page 454. Sockets can cause ground bounce voltage to increase by as much as 100%. You can often dramatically reduce the ground bounce on the PCB by eliminating sockets. The length of the PCB trace has a much smaller effect on ground bounce than sockets. For PCBs with a ground plane, the voltage drop across the inductance (L3) of the PCB trace between the device and the PCB location where other devices in the system reference ground is negligible, because L3 is significantly less than L2. The inductance in a 3-inch trace increases ground bounce for a quiet output by approximately 100 mV. Therefore, trace length should be kept to a minimum. As traces become longer, transmission line effects may cause other noise problems.

You can also reduce ground bounce due to PCB trace inductance by using multi-layer PCBs that provide separate  $V_{CC}$  and GND planes. Wirewrapping the  $V_{CC}$  and GND supplies usually increases the amount of ground bounce. To reduce unwanted inductance, you should use low-inductance bypass capacitors between the  $V_{CC}$  supply pins and the board GND plane, as close to the package supply pins as possible. A standard decoupling capacitor (0.02  $\mu F$ ) used in parallel with a high-frequency decoupling capacitor (470 pF is a standard value) gives the best results.

#### References

Knack, Kella. Debunking High-Speed PCB Design Myths. ASIC & EDA, Los Altos: James C. Uhl, July 1993.

456

Altera Corporation

■ 0595372 0005108 T73